# PERFORMANCE EVALUATION OF THE SECOND GENERATION CURRENT CONTROLLED CONVEYOR (CCCII) AND ANALYSIS OF SIMPLE VOLTAGE AND CURRENT AMPLIFIER BASED ON IT

## Nupur Mittal<sup>1</sup>, Imran Ullah Khan<sup>2</sup>, Firdaus Majeed<sup>3</sup>, Md. Amir Ansari<sup>4</sup>

<sup>1,3 & 4</sup> Assistant Professor, Dept. Electronics & Comm. Eng., Integral University, Lucknow, Uttar Pradesh, India

<sup>2</sup>Jr.Associate Professor, Dept. Electronics & Comm. Eng., Integral University, Lucknow, Uttar Pradesh, India mittalnupur2004@gmail.com, imranuk79@gmail.com, Firdausmajeed11@gmail.com, aamir.elex@gmail.com

Abstract- This paper describes the architecture of second generation current conveyor (CCCII)and designing an amplifier using second generation current conveyor. The designed amplifier through CCCII+ can be used in various analog computation circuits and is superior in performance than the classical opamp. It provides better gain with higher accuracy. The presented approach over here is to design current amplifiers and voltage amplifiers using current controlled current conveyor (CCCII). The second generation CCCII has the advantage of electronic adjustability over the CCII i.e. in CCCII, the X-terminal intrinsic resistance can be adjusted through a bias current is possible. The CCCII has been designed to work both as current amplifier and voltage amplifier. Various simulations have been carried out to obtain the desired results.

Key words: Amplifier, Current controlled conveyor, DOCCCII, Tunable current amplifier, Tunable voltage amplifier.

### I. INTRODUCTION

In the field of signal processing Current conveyors are most promising device and have the features like high bandwidth, greater linearity, larger dynamic range, low power consumption, simple circuitry and occupy less chip area. The second generation current controlled conveyor (CCCII) has the advantage of electronic adjustability over the CCII i.e. in CCCII; adjustment of the X-terminal intrinsic resistance via a bias current is possible. The CCCII has been designed to work both as current amplifier and voltage amplifier. Various simulations have been carried out to obtain the desired results. The *outcomes show good results and an amplified waveform has been obtained in both the cases.*

#### II. THE SECOND GENERATION CURRENT CONVEYOR (CCII)

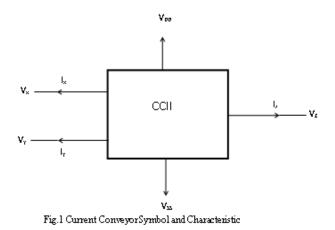

The second-generation current-conveyor was developed by Sedra in 1970. A current conveyor is a building block similar to an operational amplifier and capacitors and diodes, can implement several useful analog sub-systems such as amplifiers, integrators, and rectifiers. which, when used in conjunction with other components such as resistors, The second generation current conveyor is a three terminal device. Its symbol is shown in figure 1.

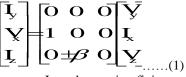

The current conveyor's response is given by equat ion

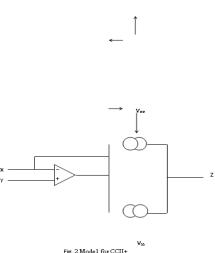

Impedance is finite and must be taken into consideration in the circuit design. When a voltage is applied at node Y, that voltage is replicated at node X. This is similar to the virtual short on an op-amp. Also when a current is injected into node X, that same current gets copied into node Z. The notation CCII+ denotes a positive Z output current conveyor (= +1) whereas CCII- denotes a negative Z output current conveyor (= - 1). Thus the terminal Y exhibits infinite input impedance. The voltage at X follows that applied to Y, thus X exhibits zero input impedance. The current supplied to X is conveyed to the high impedance output terminal Z where it is supplied with either positive polarity (in CCII+) or negative polarity (in CCII-). One model used to analyze a CCII+ is shown in figure 2. The op-amp in unity-gain feedback configuration ensures that  $V_x$  is equal to  $V_y$ , and the current mirrors ensure that  $I_z$  is equal to  $I_x$ . Here the op-amp's output stage has infinite output impedance.

#### **III. AMPLIFIER & Its ANALYSIS**

#### A. Tunable Voltage Amplifier

An electronic circuit whose function is to accept an input voltage and produce a magnified accurate replica of this voltage as an output voltage. The voltage gain of the amplifier is the amplitude ratio of the output voltage to the input voltage.

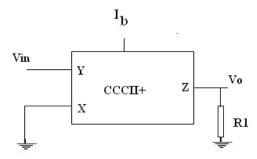

Fig.3 Circuit of Tunable Voltage Amplifier

The analysis of the amplifier circuit [9] shown in Figure 3 is as follows;

We know for CCCII+

| $V_{Y} = V_{X} + I_{X}R_{X}$                         | (2)   |

|------------------------------------------------------|-------|

| Since $V_X = 0$ , $V_Y = V_{IN}$                     | (3)   |

| $V_0 = I_Z R_1 = I_X R_1$<br>$V_0 = V_{IN}(R_1/R_X)$ | · · · |

Where  $R_X$  depends on bias current  $I_{b.}$

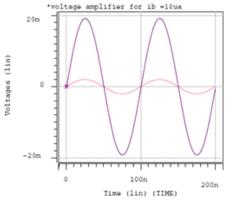

For realization, of the above voltage amplifier, CMOS design of CCCII+ is adopted, and the voltage amplifier of figure 3 is simulated on HSPICE .The input voltage is applied at node Y of the CCCII+ of the magnitude of 4mV peak to peak. The output is seen on Z+ node of the conveyor. The bias current  $I_b$  is taken as  $10\mu$ A.The simulation results of the voltage amplifier are presented in Figure 4. The output obtained after

www.ijtra.com Volume 2, Issue 6 (Nov-Dec 2014), PP. 107-110 the simulation is of value 38.4mV (peak to peak). The output is seen on Z+ node of the conveyor. The bias current  $I_b$  is taken as 10µA and theoretically 10 is selected as the gain of the voltage amplifier.

The simulation results of the voltage amplifier are presented in Figure 4. The output obtained after the simulation is of value 38.4mV (peak to peak) that means the practical value of gain is 9.6.

Fig. 4 Graph for Transient Response of Amplifier for f=10MHz

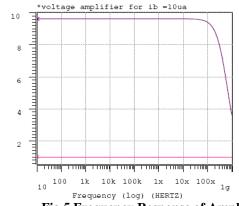

Figure 5 shows the frequency response of the above mentioned amplifier. AC analysis is performed to know about the bandwidth which is an important parameter and can be determined as the frequency at which the power of the load is at least 50%. This condition in absolute units corresponds to 70.7% and 3 dB in decibels units.

Volts Mag (lin)

В.

**Fig.5 Frequency Response of Amplifier** *Tunable current amplifier*

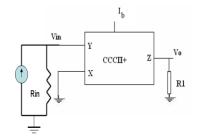

Fig.6 Circuit of Tunable Current Amplifier

The analysis of the current amplifier circuit shown in fig 6 is as follows

#### International Journal of Technical Research and Applications e-ISSN: 2320-8163,

| We know for CCCII+<br>$V_Y = V_X + I_X R_X$ (6) |

|-------------------------------------------------|

| Since V <sub>X</sub> =0,                        |

| $V_{\rm Y} = I_{\rm X} R_{\rm X} = I_{\rm IN} R_{\rm IN} \dots \dots$ |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| $I_X = I_{IN} R_{IN}/R_X = I_Z$                                                                                                                                             |   |

| Current Gain $A=I_Z/I_{IN}=R_{IN}/R_X$ (9)                                                                                                                                  | ) |

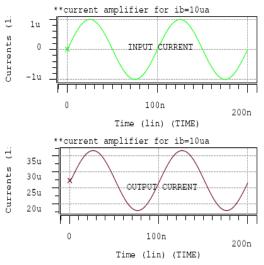

For realization, of the above current amplifier, CMOS design of CCCII+ is adopted, and the current amplifier of fig 6 is simulated on HSPICE .The input current is applied at node Y of the CCCII+ of the magnitude of  $2\mu$ A peak to peak. The output is seen on Z+ node of the conveyor. The bias current I<sub>b</sub> is taken as  $10\mu$ A. The simulation results of the current amplifier are presented in Fig 7. The output obtained after the simulation is of value 18.8  $\mu$ A (peak to peak).

Fig. 7 Transient analysis for current amplifier

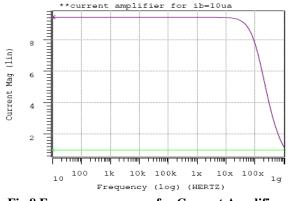

Figure 8 given below shows the frequency response of the above mentioned amplifier. AC analysis is performed to know about the bandwidth which is an important parameter and can be determined as the frequency at which the power of the load is at least 50%. This condition in absolute units corresponds to 70.7% and 3 dB in decibels units.

Fig 8 Frequency response for Current Amplifier

IV. SIMULATION & IMPLEMENTATION RESULTS Some Simulation results shown above in Figures 4, 5, 7 & 8 respectively.

www.ijtra.com Volume 2, Issue 6 (Nov-Dec 2014), PP. 107-110

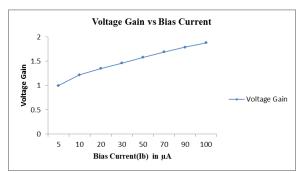

Table 1 shows values of the voltage gain with bias current in  $\mu A$  The graph shown below in figure 9 is plotted across the voltage gain to the device bias current in  $\mu A$ . As can been seen from the graph that the voltage gain increases with the increase in device bias current  $I_b.$  As bias current varies from 0  $\mu A$  to

100  $\mu$ A, voltage gain increases from 1.1 to 1.8.

| Table 1- voltage gain vs Dias Current |                |              |  |

|---------------------------------------|----------------|--------------|--|

| S.No.                                 | Bias           | Voltage Gain |  |

|                                       | Current(Ib) in |              |  |

| 1                                     | 5              | 1.1          |  |

| 2                                     | 10             | 1.22         |  |

| 3                                     | 20             | 1.35         |  |

| 4                                     | 30             | 1.46         |  |

| 5                                     | 50             | 1.58         |  |

| 6                                     | 70             | 1.69         |  |

| 7                                     | 90             | 1.77         |  |

| 8                                     | 100            | 1.8          |  |

Table 1-Voltage gain Vs Bias Current

Fig. 9. Graph between Voltage Gain & Bias Current, R1=1K constant

#### V. CONCLUSION

Current-mode circuits are undoubtedly the most widely accepted operational devices in continuous time and current mode signal processing. In addition a number of novel circuit functions such as amplifier, integrator, summer, differentiator, etc. and topologies like filters and oscillator have been explored on a front of current mode analogue circuits, opening up wider area of interest.

The circuit of CCCII+ is verified through HSPICE simulation results. The circuit of CCCII+ and the designed amplifier is verified through HSPICE simulation results.

#### REFERENCES

- C. Toumazou, F. J. Lidgey, and D. G. Haigh, 'Analogue IC design: the current-mode approach', London: Peter Peregrinus, 1990.

- [2] Fabre, A, 'Third-generation current conveyor: A new helpful active element', Elec. Letters, Vol. 31, No.5, pp. 338-339, Mar. 1995

- [3] Ahmed A. El-Adawy et al,"A Novel Fully Differential Current Conveyor and Applications for Analog VLSI", IEEE transactions on circuits and systems-ii: analog and signal digital processing, Vol. 47, No. 4, April 2000.

- [4] Awad, A., Soliman, A. M. "Inverting second generation current conveyor the missing building block, CMOS realizations and applications", Int. JL electonics,86(5), 414–432, 1999.

- [5] Awad, I. A., Soliman, A. M. "New CMOS Realization of the CCII-", IEEE trans. Circuit Syst., Vol. 46, No 4, pp. 460-463, 1999.

- [6] Barthelemy, H., Fabre, A. "A second generation currentcontrolled conveyor with negative intrinsic resistance", IEEE Trans. Circuits and Systems-I, 49(1), 63–65, 2002.

- [7] Bohr. M, S.S. Ahmed, S.U. Ahmed, M. Bost, T. Ghani, J. Greason, R. Hainsey, C. Jan, P. Packan, S.Sivakumar, S. Thompson, J. Tsai, and S. Yang, IEDM Technical Digest, p. 847, 1996.

- [8] Majeed Firdaus, Yasin.M.Y., "Low Voltage Low Power Redesign of CCCII in 45nm CMOS Technology and its Analog and Digital Applications "thesis report, Integral University,Lucknow, 2011.

- [9] Ferri, Giuseppe and Guerrini, Nicola C."Low voltage low power CMOS Current Conveyors" Kluwar A.P. pp. 2-12.

- [10] Fabre, A. "Third generation current conveyor: A new helpful active element", Electron. Lett., 31(5), 338–339, 1995.